## Friedrich-Alexander-Universität Erlangen-Nürnberg

## Lehrstuhl für Technische Elektronik Prof. Dr.-Ing. Dieter Seitzer

# Layer-3-Decoder in 3V-Technik

## Studienarbeit im Fach Elektrotechnik

vorgelegt von

cand. ing. Herbert Thoma

geb. am 25. 03. 1970 in Würzburg

Betreuer: Dipl. Ing. Stefan Krägeloh

Dipl. Ing. Harald Popp

Fraunhofer Institut für Integrierte Schaltungen

Beginn der Arbeit: 15. Mai 1995

Abgabe der Arbeit: 30. Oktober 1995

# Zusammenfassung

Im Rahmen dieser Studienarbeit wurde ein Decoder für MPEG-Audio-Layer-3 codierte Tonsignale entwickelt, der an der parallelen Druckerschnittstelle eines IBM-kompatiblen PCs betrieben wird.

Der Decoder verwendet den maskenprogrammierten Signalprozessor MAS 3503 C. Die Schaltung ist zur Minimierung des Stromverbrauchs in gemischter 3 V- / 5 V- Technik realisiert.

Die PC-Software ermöglicht das Abspielen von Layer-3-Files und den Austausch von Status- und Steuerinformationen mit dem MAS 3503 C über dessen I<sup>2</sup>C-Bus Schnittstelle.

## **Abstract**

This dissertation presents a decoder for MPEG-Audio-Layer-3 bitstreams which operates on a printer port of a PC.

The decoder is based on the MAS 3503 C DSP. A mixed 3 V/5 V design was developed to minimize power comsumption.

PC software provides abilities to play layer-3-files and to interchange status and control data with the MAS 3503 C via an I<sup>2</sup>C bus interface.

# Erklärung

Ich versichere, daß ich die Arbeit ohne fremde Hilfe und ohne Benutzung anderer als der angegebenen Quellen angefertigt habe und daß die Arbeit in gleicher oder ähnlicher Form noch keiner anderen Prüfungsbehörde vorgelegen hat und von dieser als Teil einer Prüfungsleistung angenommen wurde. Alle Ausführungen, die wörtlich oder sinngemäß übernommen wurden, sind als solche gekennzeichnet.

| Erlangen. | den   | 30  | 10  | 1995   |  |  |

|-----------|-------|-----|-----|--------|--|--|

| глиануси. | CICII | ov. | TO. | 1330 - |  |  |

# Aufgabenstellung

## Layer-3-Decoder in 3 V-Technik

Am IIS existiert ein Layer-3-Decoder auf Basis des maskenprogrammierten Signalprozessors MAS 3503 C von Intermetall. Er wird z. B. auf einer Adapterkarte eingesetzt, um über die parallele Druckerschnittstelle eines Rechners Layer-3-codierte Dateien an einer Stereoanlage wiedergeben zu können. Die derzeitige Schaltung ist in 5 V-Technik realisiert und nimmt ca. 300 mA Strom auf.

Zur Vorbereitung von Mobilanwendungen soll der Decoder nun in 3 V-Technik realisiert werden. Hierzu sind u. a. folgende Aufgaben zu erfüllen:

- Schaltungsdesign mit 3 V-Komponenten

- Aufbau eines Prototyps als Funktionsmuster

# Inhaltsverzeichnis

| 1. | Einl | eitung   |                                      | 1  |

|----|------|----------|--------------------------------------|----|

|    | 1.1  | Bisher   | riger Stand und Aufgabenstellung     | 1  |

|    | 1.2  | Gliede   | erung der Arbeit                     | 2  |

| 2. | Gru  | ndlagei  | n                                    | 3  |

|    | 2.1  | Gehör    | angepaßte Audiokodierung             | 3  |

|    |      | 2.1.1    | Psychoakustik                        | 3  |

|    |      | 2.1.2    | Coder und Decoder                    | 4  |

|    |      | 2.1.3    | Der MPEG-Audio Standard              | 5  |

|    | 2.2  | MAS      | 3503 C                               | 6  |

|    | 2.3  | l²C-Βι   | us                                   | 7  |

| 3. | Rea  | lisierun | $\mathbf{g}$                         | 10 |

|    | 3.1  | Hardw    | vare                                 | 10 |

|    |      | 3.1.1    | Stromversorgung                      | 11 |

|    |      | 3.1.2    | Treiber zur Centronics-Schnittstelle | 12 |

|    |      | 3.1.3    | Digital-Analog-Wandler               | 13 |

|    |      | 3.1.4    | MASC, Fifo und Programmierbare Logik | 15 |

|    |      | 3.1.5    | Funktionsweise des PLDs              | 19 |

|    |      | 3.1.6    | Externe Verbindungen                 | 22 |

|    | 3.2  | Softwa   | are                                  | 24 |

|    |      | 3.2.1    | Bedienung der Software               | 24 |

|    |      | 3.2.2    | Kommandozeilenoptionen               | 25 |

|    |      | 3.2.3    | Programmbeschreibung                 | 27 |

### In halts verzeichn is

| 4.  | Erge   | ebnisse                                          | 29 |

|-----|--------|--------------------------------------------------|----|

|     | 4.1    | Stromversorgung                                  | 29 |

|     | 4.2    | Audioqualität des DACs                           | 31 |

|     | 4.3    | Erfahrungen mit Hard- und Software               | 33 |

| 5.  | Zusa   | ammenfassung und Ausblick                        | 35 |

|     | 5.1    | Technische Daten                                 | 35 |

|     | 5.2    | Verbesserte Stromversorgung                      | 35 |

|     | 5.3    | Preiswertere Version des Decoders                | 36 |

|     | 5.4    | Fazit                                            | 37 |

| Αb  | kürzı  | ungen                                            | 38 |

| Lit | teratu | rverzeichnis                                     | 39 |

| An  | nhang  |                                                  | 41 |

| Α.  | Hard   | lware                                            | 43 |

|     | A.1    | Schaltplan                                       | 43 |

|     | A.2    | Layout                                           | 43 |

|     | A.3    | Bauteiledaten                                    | 43 |

|     | A.4    | Beschreibung des Programmierbaren Logikbausteins | 50 |

|     |        | A.4.1 Logische Beschreibung                      | 50 |

|     |        | A.4.2 Bausteinabhängige Beschreibung             | 69 |

|     |        | A.4.3 Design-Implementierung                     | 72 |

| В.  | C-P    | rogramme                                         | 75 |

|     | B.1    | Aufteilung der C-Funktionen auf Dateien          | 75 |

|     | B.2    | Programm-Listings                                | 76 |

|     |        | B.2.1 lpt.c                                      | 76 |

|     |        | B.2.2 cmdline.h                                  | 84 |

|     |        | B.2.3 cmdline.c                                  | 85 |

|     |        | B.2.4 display.h                                  | 90 |

|     |        | B.2.5 display.c                                  | 92 |

#### In halts verzeichn is

|    |      | B.2.6   | $masccent.h \dots \dots$ | 96  |

|----|------|---------|--------------------------------------------------------------------------------------------------------------------------------|-----|

|    |      | B.2.7   | masccent.c                                                                                                                     | 97  |

|    |      | B.2.8   | iic.h                                                                                                                          | 102 |

|    |      | B.2.9   | iic.c                                                                                                                          | 103 |

|    |      | B.2.10  | $iicmasc.h \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                            | 107 |

|    |      | B.2.11  | $iicmasc.c \ . \ . \ . \ . \ . \ . \ . \ . \ . $                                                                               | 108 |

| C. | Prei | swertei | re Version des Decoders                                                                                                        | 112 |

|    | C.1  | Geänd   | erter Schaltplan                                                                                                               | 112 |

|    | C.2  | Beschr  | reibung des PLDs                                                                                                               | 112 |

|    |      | C.2.1   | Logische Beschreibung                                                                                                          | 115 |

|    |      | C.2.2   | Bausteinabhängige Beschreibung                                                                                                 | 127 |

|    |      | C23     | Design-Implementierung                                                                                                         | 129 |

# Abbildungsverzeichnis

| 2.1  | Mithörschwellen                                 |

|------|-------------------------------------------------|

| 2.2  | Blockdiagramm eines gehörangepaßten Audiocoders |

| 2.3  | MASC Blockdiagramm                              |

| 2.4  | MASC Eingangsinterface                          |

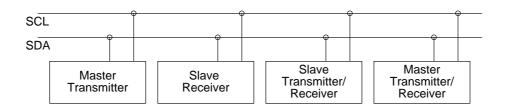

| 2.5  | I <sup>2</sup> C-Bus                            |

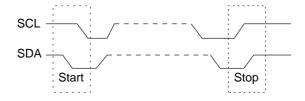

| 2.6  | Start- und Stopbedingung                        |

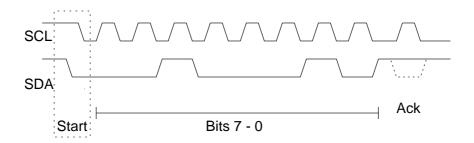

| 2.7  | Datentransfer                                   |

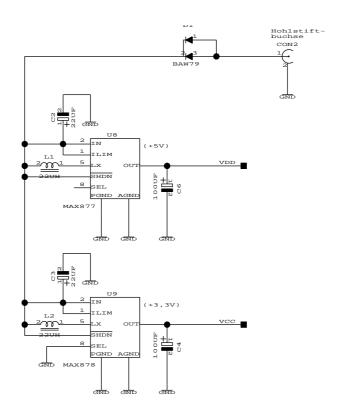

| 3.1  | Stromversorgung                                 |

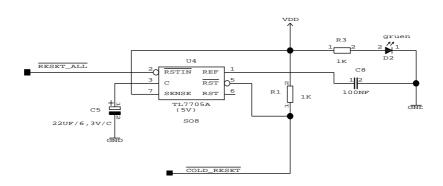

| 3.2  | Erzeugung des Resetsignals                      |

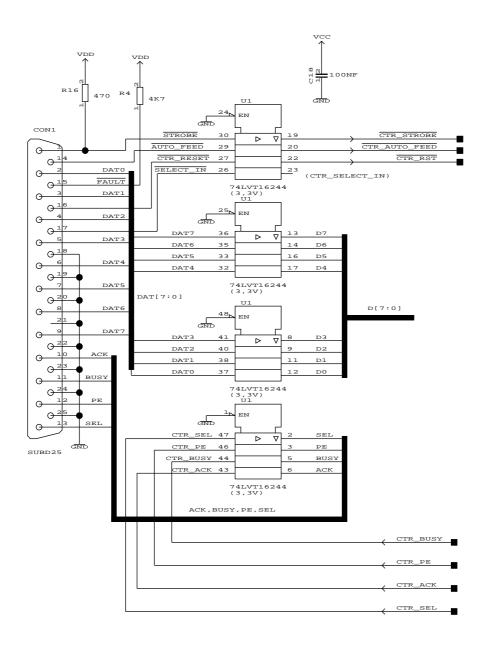

| 3.3  | Centronics-Buffer                               |

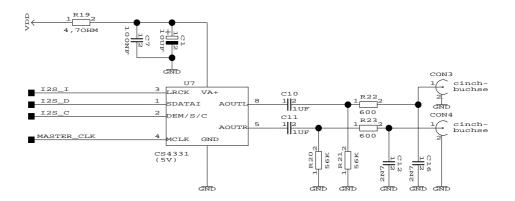

| 3.4  | Digital-Analog-Wandler                          |

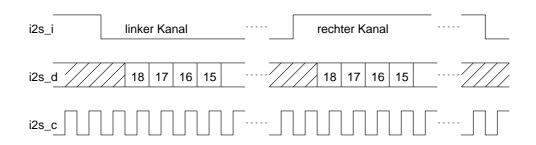

| 3.5  | I <sup>2</sup> S-Format                         |

| 3.6  | Konfiguration des DACs                          |

| 3.7  | MASC                                            |

| 3.8  | PLD und Fifo                                    |

| 3.9  | Blockdiagramm des PLDs                          |

| 3.10 | Zustandsdiagramm der parallel-seriell Wandlung  |

| 3.11 | Typischer Bildschirm                            |

| 3.12 | Programmstruktur                                |

| 4.1  | Regelung der Versorgungsspannungen              |

| 4.2  | Störungen auf den Versorgungsspannungen         |

| 4.3  | Stromaufnahme                                   |

| 4.4  | Frequenzgang des DACs                           |

| 4.5  | Ausgangsspektrum bei digital Null am Eingang    |

### Abbildungs verzeichnis

| 4.6 | Verzerrungen des DACs          | 33  |

|-----|--------------------------------|-----|

| 5.1 | Verbesserte Stromversorgung    | 36  |

| A.1 | Schaltplan (Teil 1)            | 44  |

| A.2 | Schaltplan (Teil 2)            | 45  |

| A.3 | Layout Oberseite               | 46  |

| A.4 | Layout Innenlage 1             | 46  |

| A.5 | Layout Innenlage 2             | 47  |

| A.6 | Layout Unterseite              | 47  |

| A.7 | Bauteileplazierung Oberseite   | 48  |

| A.8 | Bauteileplazierung Unterseite  | 48  |

| C.1 | Geänderter Schaltplan (Teil 1) | 113 |

| C.2 | Geänderter Schaltplan (Teil 2) | 114 |

# **Tabellenverzeichnis**

| 2.1 | Ubersicht der Layer                                     | 5  |

|-----|---------------------------------------------------------|----|

| 3.1 | Stromverbrauch der Bauteile                             | 10 |

| 3.2 | Abtastraten                                             | 17 |

| 3.3 | Konfigurationsregister                                  | 20 |

| 3.4 | Belegung von J1                                         | 23 |

| 3.5 | Belegung von J2                                         | 23 |

| 3.6 | Konfiguration des DACs                                  | 26 |

| 4.1 | Verbindung mit UPD                                      | 31 |

| 4.2 | Einstellungen des UPDs                                  | 31 |

| 5.1 | Technische Daten                                        | 35 |

| 5.2 | Zusätzliche Widerstände für verbesserte Stromversorgung | 36 |

| A.1 | Bauteileliste                                           | 49 |

| B.1 | C-Deklarations-Dateien                                  | 75 |

| B 2 | C-Definitions-Dateien                                   | 76 |

# 1. Einleitung

Sowohl der Lehrstuhl für Technische Elektronik der Universität Erlangen als auch das Institut für Integrierte Schaltungen der Fraunhofer-Gesellschaft betreiben seit Jahren Forschung auf dem Gebiet der Quellencodierung von Audiosignalen. Ergebnisse dieser Forschungsarbeiten sind in einen internationalen Standard, den sogenannten MPEG-Standard [1] eingeflossen.

Im Rahmen dieser Arbeiten ist am IIS ein Decoder für MPEG-codierte Audiodaten entwickelt worden, der an der Druckerschnittstelle eines IBM-PC kompatiblen Rechners betrieben werden kann.

Das Ziel dieser Studienarbeit ist die Entwicklung einer verbesserten Version dieses Decoders.

## 1.1 Bisheriger Stand und Aufgabenstellung

Der vorhandene Decoder besteht im wesentlichen aus dem maskenprogrammierten Signalprozessor MAS 3503 C (im folgenden kurz MASC genannt) und zugehörigem Digital-Analog-Wandler, einem Fifo und einer Steuerlogik, die in einem progammierbaren Logikbaustein vom Typ ispLSI 1016 untergebracht ist. Die Schaltung ist in 5 V-Technik aufgebaut und nimmt ca. 300 mA Strom auf. Zur Ansteuerung des Decoders vom PC aus steht ein einfaches, kommandozeilengesteuertes Programm zur Verfügung. Dieser Decoder wird von der Firma Proton Data hergestellt und vertrieben.

Im Rahmen dieser Studienarbeit soll nun eine neue Schaltung entwickelt werden, die folgende Eigenschaften aufweisen soll:

- Die Schaltung soll zur Reduzierung des Stromverbrauchs in 3 V-Technik realisiert werden. Es ist auch ein Entwurf in gemischter 3 V/5 V-Technik möglich, wenn wichtige Bauteile nicht in 3 V Versionen verfügbar sind.

- Die Betriebsspannung soll mit Schaltreglerbausteinen erzeugt werden, um eine Versorgung aus Akkumulatoren zu ermöglichen.

#### 1. Einleitung

- Der MASC enthält eine I<sup>2</sup>C-Bus Schnittstelle, über die diverse Status- und Steuerinformationen mit dem MASC ausgetauscht werden können. Diese Schnittstelle soll nutzbar gemacht werden.

- Als Digital-Analog-Converter soll ein CS 4431 eingesetzt werden. Die technischen Daten dieses Bausteins sind zu ermitteln.

Das eigentliche Codierverfahren ist nicht Thema dieser Arbeit. Die Audiocodierung nach dem MPEG-Standard wurde über mehrere Jahre von verschiedenen Forschungseinrichtungen entwickelt, die entsprechenden Algorithmen sind in dem hier verwendeten MASC-Prozessor implementiert.

## 1.2 Gliederung der Arbeit

Nachdem in diesem ersten Kapitel zunächst die Aufgabenstellung präzisiert wurde, wird das nächste Kapitel wichtige Grundlagen der Arbeit darstellen. Dies umfaßt sowohl Ausführungen über gehöhrangepaßte Audiocodierung und den MPEG-Audio-Standard, als auch Details über verwendete Bauelemente.

Kapitel 3 zeigt die Einzelheiten der Schaltung und der PC-Software an Hand von Schaltbildern und Struktogrammen. Meßergebnisse und Erfahrungen mit dem gebauten Decoder sind schließlich in Kapitel 4 dargestellt.

In Kapitel 5 werden die Ergebnisse noch einmal zusammengefaßt und einige kleine Änderungsvorschläge gemacht, die vor allem für die künftige Serienproduktion des Decoders von Bedeutung sind.

## 2. Grundlagen

## 2.1 Gehörangepaßte Audiokodierung

Der Qualitätsstandard bei der Übertragung und Speicherung von Tonsignalen wird heute durch CD- bzw. DAT-Geräte gesetzt, die mit 16 bit linearer Quantisierung und Abtastraten von 44,1 kHz bzw. 48 kHz arbeiten. Damit ergeben sich Datenraten von 1411 kbps bzw. 1536 kbps für ein Stereosignal. Dies entspricht einem Speicherbedarf von ca. 11 MByte für 1 Minute Musik.

Für Anwendungen wie den digitalen terrestrischen Hörrundfunk (DAB) oder die digitale Compactcasette (DCC) stehen jedoch die für die Übertragung derartiger Bitraten nötigen Bandbreiten nicht zur Verfügung. Es ist eine Reduzierung der Bitrate um den Faktor 4 bis 8 erforderlich. Bei einer Reduzierung der Bitrate um den Faktor 12 gelingt die Übertragung eines Stereosignals über eine normale ISDN-Verbindung mit 128 kbps in CD-Qualität.

Kodierverfahren, die derartig hohe Kompressionsfaktoren erreichen, nutzen zusätzlich zu aus der Informationstheorie bekannten Verfahren zur Redundanzreduktion die Eigenschaften des menschlichen Gehörs zur Irrelevanzreduktion aus. Es handelt sich also um nicht verlustfreie Kodierverfahren, das heißt aus den kodierten Daten können die ursprünglichen Daten nicht exakt rekonstruiert werden, ein Mensch kann den Unterschied zwischen originalen und kodierten Tonsignalen jedoch nicht hören.

### 2.1.1 Psychoakustik

Die Psychoakustik befaßt sich mit den Eigenschaften des menschlichen Ohrs als Empfänger für Schallereignisse. Viele Erkenntnisse der Psychoakustik gehen auf Prof. Zwicker zurück [10].

Das Gehör reagiert auf Schall nicht objektiv wie ein Meßgerät. Bei der Wahrnehmung treten einige Phänomene auf, die sich zur Datenreduktion nutzen lassen. Die Empfindlichkeit des Ohrs ist nicht bei allen Frequenzen gleich, sondern erreicht bei etwa 4 kHz ein Maximum und fällt zu den Bandgrenzen des Ohrs bei 20 Hz und 20 kHz ab. Dieses Verhalten wird mit der Ruhehörschwelle beschrieben.

#### 2. Grundlagen

Am wichtigsten für die Audiokodierung ist der sogenannte Verdeckungseffekt. Die Verdeckung bewirkt, daß ein leiser Ton bei Auftreten eines lauteren Tons nicht mehr wahrgenommen werden kann. Der lautere Ton wird hierbei als Maskierer bezeichnet. Der Verdeckungseffekt wurde in aufwendigen Hörtests für unterschiedliche Maskierer untersucht. Für jeden Maskierer ergibt sich eine sogenannte Mithörschwelle. Signalanteile, die unterhalb der Mithörschwelle liegen, können vom Ohr nicht wahrgenommen werden und müssen folglich auch nicht übertragen werden.

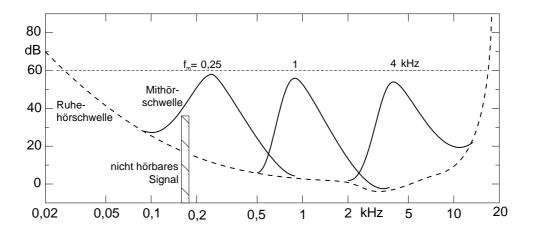

Abbildung 2.1: Mithörschwellen

Die Verdeckung des leiseren Tons kann zeitgleich, nach und sogar vor dem Auftreten des Maskieres erfolgen, entsprechend spricht man von Simultan-, Nach- und Vorverdeckung. Die Abbildung 2.1 zeigt die Ruhehörschwelle und den Verlauf der Mithörschwellen für unterschiedliche Frequenzen des Maskierers bei Simultanverdeckung.

#### 2.1.2 Coder und Decoder

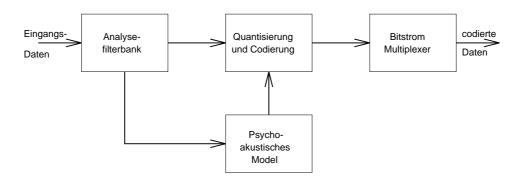

Die Abbildung 2.2 zeigt das Blockschaltbild eines gehörangepaßten Audiocoders. Die Tonsignale werden zuerst durch eine Filterbank in verschiedene Frequenzbänder zerlegt. Die einzelnen Bänder werden unterabgetastet und getrennt quantisiert, und zwar so, daß das durch die Quantisierung erzeugte Quantisierungsrauschen unter der errechneten Mithörschwelle bleibt.

Der Block Bitstrom Multiplexer fügt die Werte der Teilbänder und eventuelle Zusatzdaten zu einem Datenstrom zusammen.

Der Decoder ist weit weniger komplex, da er nur aus den einzelnen quantisierten Frequenzanteilen ein Tonsignal rekonstruieren muß und keine Rechenleistung für

Abbildung 2.2: Blockdiagramm eines gehörangepaßten Audiocoders

die Psychoakustik braucht.

### 2.1.3 Der MPEG-Audio Standard

Im MPEG Audio Standard [1] sind drei verschiedene, aufeinander aufbauende gehörangepaßte Toncodierverfahren, die sogenannten Layer beschrieben. Von Layer 1 zu Layer 3 steigen die Komplexität und die Qualität des Verfahrens bei niedrigen Bitraten. Normalerweise kann ein Layer 3 Decoder auch die Layer 1 und 2, ein Layer 2 Decoder auch den Layer 1 verarbeiten.

| Layer | Kompressionsfaktor | Beispielanwendung |

|-------|--------------------|-------------------|

| 1     | ca. 4              | DCC               |

| 2     | ca. 6–8            | DAB               |

| 3     | ca. 10–12          | SaRa              |

Tabelle 2.1: Übersicht der Layer

Tabelle 2.1 zeigt die bei den einzelnen Layern ohne hörbare Störungen erreichbaren Kompressionsfaktoren sowie je eine Beispielanwendung.

Zusätzlich zu den Audiodaten kann der MPEG-Audio Standard Zusatzdaten übertragen, die Ancillary Data genannt werden. Damit ist es zum Beispiel möglich Titel und Interpreten des codierten Musikstücks zu übermitteln.

### 2.2 MAS 3503 C

Die Prozessorfamilie MAS 3500 von ITT-Intermetall ist eine Familie von maskenprogammierten digitalen Signalprozessoren, die speziell für die Verarbeitung von Standard-Audiosignalen und datenreduzierten Audiostandards sowie digitale Modulation/Demodulation entwickelt wurde. Die Mitglieder der Familie unterscheiden sich in der Größe des integrierten Speichers, den Schnittstellen und natürlich durch das Programm im ROM.

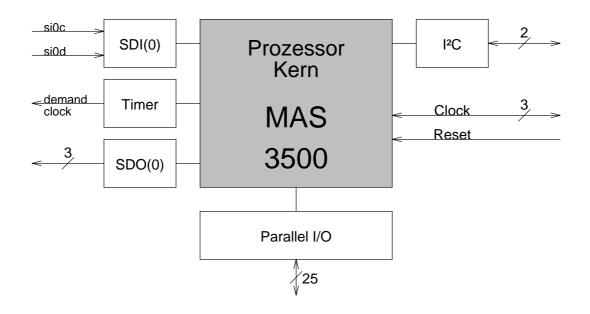

Mit dem MAS 3503 C ist ein Decoder für Layer-3-codierte Audiosignale realisiert. Abweichend vom MPEG-Standard können ohne zusätzliche Maßnahmen nur Layer-3 Daten decodiert werden, die Layer 1 und 2 werden nicht unterstützt. Im Folgenden wird der MAS 3503 C kurz mit MASC bezeichnet. Bild 2.3 zeigt sein Blockdiagramm mit dem Prozessorkern und den verschiedenen Schnittstellen.

Mit dem Prozessorkern ist eine sehr leistungsfähige Signalprozessorarchitektur realisiert. Die Wortbreite beträgt 20 bit, der MASC verfügt über 6 k Worte ROM und 4 k Worte Ram.

Abbildung 2.3: MASC Blockdiagramm

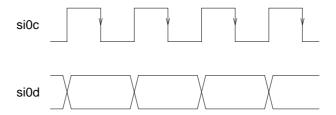

Um den Prozessorkern sind die Schnittstellen gruppiert. Der Block SDI(0) stellt einen synchronen seriellen Eingang dar, über den der MASC die Layer-3-codierten Daten erhält. Der MASC übernimmt die Daten an si0d jeweils bei der fallenden Flanke von si0c (siehe Abbildung 2.4). Die maximale Taktfrequenz beträgt 2 MHz.

Der MASC unterscheidet 2 Betriebsmodi: Im Sync-Mode werden die Eingangsdaten kontinuierlich mit einer festen Bitrate geliefert, im Demand-Mode fordert der

Abbildung 2.4: MASC Eingangsinterface

MASC selbst je nach Bedarf neue Daten an. Am Ausgang demand clock steht ein Takt zur Verfügung, der im Demand-Mode als Eingangstakt verwendet werden kann.

SDO(0) ist ein serieller digitaler Ausgang, der konfiguriert werden kann, um verschiedene zur Ansteuerung von Digital-Analog-Umsetzern geeignete Datenformate zu erzeugen. Der MASC kann ein Ausgangsformat erzeugen, das mit dem ASCO-Baustein von ITT kompatibel ist, sowie ein Ausgangsformat nach dem Industriestandard I<sup>2</sup>S.

Zur Kommunikation mit einem Host-System steht dem MASC eine I<sup>2</sup>C-Bus Schnittstelle zur Verfügung, der MASC verhält sich am I<sup>2</sup>C-Bus als Slave. Die I<sup>2</sup>C-Bus Schnittstelle bietet folgende Möglichkeiten:

- Einstellen der Wiedergabelautstärke.

- Download von Programmen in das RAM des MASCs. Dadurch können auch die Layer 1 und 2 decodiert werden.

- Auslesen der im Layer-3 Bitstrom enthaltenen Header- und Ancillary-Daten.

Das Parallel I/O Interface dient beim Power Up Reset zur Initialisierung und Konfiguration des MASCs. Im laufenden Betrieb signalisiert der MASC über die Parallelschnittstelle wichtige Betriebszustände und einige Daten aus dem Header der MPEG-Daten. Außerdem wird angezeigt, ob über den I<sup>2</sup>C-Bus gültige Ancillary-Daten gelesen werden können und ob der MASC im Demand-Mode neue Daten über das serielle Eingangsinterface benötigt.

## **2.3** $I^2C$ -**Bus**

Der I<sup>2</sup>C-Bus ist ein serieller sychroner 2-Draht-Bus, der vor allem in Geräten der Unterhaltungselektronik zur Kommunikation zwischen integrierten Schaltungen, wie zum Beispiel einem zentralen Mikrocontroller und einem Fernbedienungsempfänger, eingesetzt wird. Daher leitet sich auch der Name Inter-IC-Bus ab.

#### 2. Grundlagen

Während eines Datentransfers ist ein IC der Master, der den Takt auf der Leitung SCL erzeugt, die anderen verhalten sich als Slaves. Jedes am Bus angeschlossene IC hat eine eindeutige Adresse, die aus 7 bits besteht. Wenn ein Master einen Transfer beginnt, sendet er zuerst die Adresse des ICs, mit dem er kommunizieren will. Der I<sup>2</sup>C-Bus ist ein echter Multi-Master-Bus mit Kollisionserkennung und Arbitrierung, er erlaubt also den Zugriff von mehreren Mastern ohne Datenverlust.

Abbildung 2.5: I<sup>2</sup>C-Bus

Wenn kein Datentransfer stattfindet, liegt an den Leitungen SCL und SDA High-Pegel an. Dies wird dadurch erreicht, daß die Treiber der ICs zum I<sup>2</sup>C-Bus als Open-Collector- bzw. Open-Drain-Ausgänge ausgeführt sind, die mit gemeinsamen externen Pull-Up-Widerständen beschaltet sind.

Um einen Transfer zu beginnen, erzeugt ein Master eine Startbedingung: Einen Pegelwechsel von High nach Low auf der SDA-Leitung, während SCL High ist.

Abbildung 2.6: Start- und Stopbedingung

Nach dem Datentransfer muß der Master eine Stopbedingung am Bus erzeugen (siehe Abbildung 2.6). Während des eigentlichen Datentransfers darf sich der Pegel auf der SDA-Leitung nur ändern, wenn SCL Low ist.

Wie schon erwähnt sendet der Master zuerst die 7-bittige Adresse gefolgt von einem weiteren bit, das die Richtung des nachfolgenden Datentransfers angibt. Beim folgenden 9. Taktimpuls muß das adressierte IC die SDA-Leitung zur Bestätigung auf Low ziehen. Die Datenübertragung erfolgt byteweise mit dem MSB zuerst. Auf jedes Byte folgt ein Bestätigungsimpuls vom Empfänger. Bleibt die Bestätigung aus, beendet der Master die Übertragung.

Abbildung 2.7: Datentransfer

Die maximale Taktfrequenz beträgt 100 kHz, bei neueren, sogenannten 'fast mode' ICs 400 kHz. Ist der vom Master erzeugte Takt zu schnell für ein Slave-IC, kann das Slave-IC die SCL-Leitung auf Low ziehen, was den Master veranlaßt, so lange zu warten, bis SCL wieder High wird.

Da beim hier vorgestellten Layer-3-Decoder lediglich ein Master und ein Slave verwendet werden, wird hier nicht näher auf die Mulit-Master-Fähigkeit des I<sup>2</sup>C-Busses eingegangen. Genaue Informationen dazu sowie detaillierte elektrische und Timingspezifikationen können [4] entnommen werden.

# 3. Realisierung

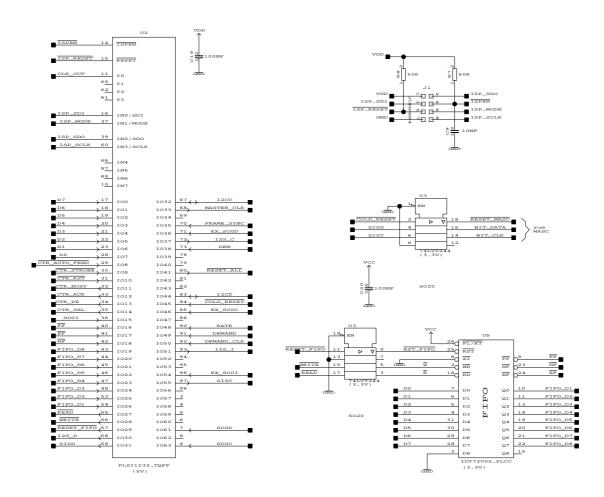

Der hier vorgestellte Layer 3 Decoder lehnt sich eng an die schon am IIS vorhandene Schaltung an. Da es also schon Erfahrungen mit den wesentlichen Bauteilen gab und diese Bauteile auch nur in SMD-Gehäusen erhältlich sind, wurde auf einen Prototypen in Wire-Wrap-Technik verzichtet und die Schaltung auf einer gedruckten Leiterplatte aufgebaut.

Auch bei der Software konnten Teile des vorhandenen Programms wiederverwendet werden. Die Schaltung des neuen Decoders ist kompatibel zu der des alten, so daß die Wiedergabe von Layer 3 Files auch mit dem alten Programm möglich ist. Die neue Software ermöglicht zusätzlich die Nutzung des I<sup>2</sup>C-Buses und sie bietet eine bessere Benutzeroberfläche.

### 3.1 Hardware

Der Vorteil der 3 V Technik liegt vor allem in der geringeren Stromaufnahme der Bauteile. Als Industriestandard hat sich eine Versorgungsspannung von 3,3 Volt durchgesetzt. Tabelle 3.1 zeigt die Datenblattangaben zum Stromverbrauch der verwendeten Bauteile bei 3,3 V und 5 V.

|             | 3,3 Volt           |                      | 5 Volt  |                   |

|-------------|--------------------|----------------------|---------|-------------------|

| Bauteil     | Strom              | Leistung             | Strom   | Leistung          |

| MASC        | 60 mA              | $200~\mathrm{mW}$    | 80 mA   | $400 \mathrm{mW}$ |

| Fifo        | 50  mA             | 165  mW              | 120  mA | 600  mW           |

| ispLSI 1032 | nicht verfügbar    |                      | 180 mA  | 900  mW           |

| DAC         | 17 mA              | 55  mW               | 20 mA   | 100  mW           |

| 7416244     | 5 mA               | $16 \mathrm{mW}$     | 72 mA   | 360  mW           |

| Summe       | $312 \text{ mA}^1$ | $1336~\mathrm{mW^1}$ | 472  mA | 2360  mW          |

Tabelle 3.1: Stromverbrauch der Bauteile

$<sup>^1\</sup>mathrm{für}$ den isp<br/>LSI 1032 wurde der Stromverbrauch des 5 Volt Typs berücksichtigt

Die Schaltung des Layer 3 Decoders konnte nicht durchgänging in 3 V Technik realisiert werden, da leistungsfähige CPLDs, wie sie hier benötigt werden, noch nicht in 3 V Ausführungen erhältlich sind. Die Schaltung ist jedoch so ausgelegt, daß sie ohne großen Aufwand auf reinen 3 V Betrieb umgestellt werden kann, sobald entsprechende CPLDs verfügbar werden.

In den folgenden Abschnitten wird die Schaltung des Layer 3 Decoders an Hand von Teilschaltbildern beschrieben. Der Gesammtschaltplan ist im Anhang auf den Seiten 44 und 45 zu finden.

### 3.1.1 Stromversorgung

Wegen des vorgesehenen Einsatzbereichs — Mobilanwendung und Versorgung aus Akkumulatoren — schied eine Stabilisierung der Versorgungsspannungen durch Linearregler wie dem 7805 aus. Da zwei Spannungen geregelt werden müssen und nur eine begrenzte Platinenfläche zur Verfügung steht, mußte auch eine platzsparende Lösung gefunden werden.

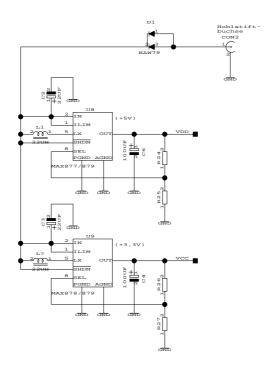

Abbildung 3.1: Stromversorgung

Die Wahl fiel auf die Schaltreglerbausteine MAX 877 bzw. MAX 878 für 5 V

#### 3. Realisierung

bzw. 3,3 V. Diese Bauteile können sowohl als Aufwärts- als auch als Abwärtsregler arbeiten und so eine Eingangsspannung zwischen 2,5 V und 6,2 V auf die gewünschte Ausgangsspannung regeln. Der Wirkungsgrad der Regler beträgt 85%. Da die Regler nur drei externe Bauelemente, zwei Kondensatoren und eine Induktivität, benötigen und im SMD-Gehäuse erhältlich sind, benötigt diese Stromversorgung auch nur wenig Platinenfläche. Abbildung 3.1 zeigt die Schaltung der Spannungsregler. Die Diode D1 dient dem Verpolungsschutz.

Zur Stromversorgung gehört auch die Erzeugung eines definierten Resetimpulses beim Einschalten der Versorgungsspannung. Diese Aufgabe erledigt ein TL 7705 A, der die 5 V Spannung überwacht. Solange diese Spannung unter 4,5 V bleibt, ist das Signal cold\_reset aktiv. Über reset\_all kann ein Reset vom PC ausgelöst werden. Abbildung 3.2 zeigt die entsprechende Teilschaltung.

Abbildung 3.2: Erzeugung des Resetsignals

#### 3.1.2 Treiber zur Centronics-Schnittstelle

Der Layer 3 Decoder wird über eine Druckerschnittstelle mit dem PC verbunden. Da im Decoder 3 V Bauteile verwendet werden, der PC aber mit 5 V Pegeln arbeitet, muß ein spezieller Treiber zur Pegelumsetzung eingesetzt werden.

Als solcher Treiber eignet sich besonders ein Baustein aus der LVT-Logikfamilie. Die ICs dieser Familie werden mit einer Spannung von 3,3 V betrieben, erlauben jedoch 5 V Pegel an den Eingängen. Auch die weiteren Eigenschaften der LVT-Familie machen sie für diesen Einsatzzweck besonders geeignet. An den Ein- und Ausgängen dieser ICs dürfen auch bei abgeschalteter Versorgungsspannung Logikpegel anliegen, daher kann der Decoder nicht beschädigt werden, wenn er am PC angeschlossen aber nicht mit einer Stromversorgung verbunden ist.

Im Layer 3 Decoder wird ein 74LVT16244 eingesetzt. Dieser Baustein enthält 16

Abbildung 3.3: Centronics-Buffer

Treiber, damit können mit nur einem IC alle Signale der Centronics-Schnittstelle gepuffert werden. In Abbildung 3.3 ist diese Teilschaltung dargestellt.

### 3.1.3 Digital-Analog-Wandler

Die Wahl für den DAC fiel auf den CS 4331 von Crystal. Dieser Baustein arbeitet nach dem Delta-Sigma Prinzip und weist eine Reihe von Vorteilen auf:

#### 3. Realisierung

- Betrieb an 5 V und 3,3 V möglich.

- Integriertes Deemphasefilter.

- Verschiedene Eingangsdatenformate einstellbar.

- Sehr kleines, 8-poliges Gehäuse.

Der Vorteil des kleinen Gehäuses wird jedoch mit einer komplizierteren Ansteuerschaltung erkauft, wenn man alle Möglichkeiten des CS 4331 nutzen will.

Abbildung 3.4: Digital-Analog-Wandler

Obwohl der CS 4331 auch an 3,3 V betrieben werden kann, wurde er in der vorliegenden Schaltung an 5 V angeschlossen, da man damit eine etwas bessere Audioqualität erreicht. Das R-C Glied aus R19, C1 und C7 unterdrückt Störungen der Versorgungsspannung.

Der DAC benötigt zum Betrieb einen Takt mit der 256-fachen Frequenz der Audio-Samplerate, diesen erhält er über die Leitung master\_clk vom PLD.

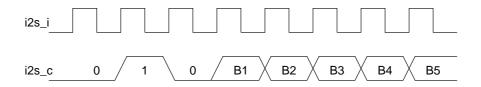

Abbildung 3.5:  $I^2S$ -Format

Die Zuführung der Audiodaten erfolgt über die Leitungen i2s\_i, i2s\_d und i2s\_c im I<sup>2</sup>S-Format. Das Signal i2s\_i ist dabei ein Rechtecksignal mit der Frequenz der

Samplerate, das angibt, ob die Audiodaten zum linken oder rechten Kanal gehören. Die eigentlichen Audiodaten werden durch i2s\_d übermittelt. Der CS 4331 erwartet 18 gültige Audiobits. An i2s\_c liegt im einfachsten Fall ein Schiebetakt an, dessen Frequenz der 64-fachen Samplerate entspricht. Bild 3.5 verdeutlicht die Zusammenhänge. Der MASC kann genau dieses Format erzeugen.

Der DAC kann sich den Schiebetakt an Hand von master\_clk und i2s\_i auch selbst erzeugen. Man erhält dann Zugriff auf das Deemphasefilter und das Konfigurationsregister. In diesem Fall erwartet der CS 4331 allerdings ein anderes Datenformat, so daß er bei jedem Reset erst konfiguriert werden muß.

Abbildung 3.6: Konfiguration des DACs

Die Konfiguration erfolgt seriell über i2s\_c, Bild 3.6 zeigt wie das Konfigurationsregister beschrieben wird. Nach einer Präambel folgen 5 bits, die das Verhalten des DACs festlegen. Der DAC übernimmt jedes bit bei der fallenden Flanke von i2s\_i. Die Bedeutung der einzelnen bits wird in 3.2.2 auf Seite 26 erläutert.

Liegt an i2s\_c ein konstanter Low-Pegel an, so ist das Deemphasefilter aktiv, bei High-Pegel ist es inaktiv.

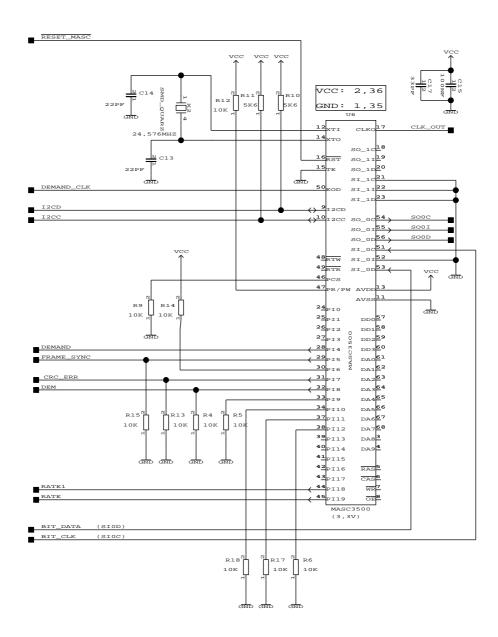

### 3.1.4 MASC, Fifo und Programmierbare Logik

Der MASC ist das Herzstück des Layer 3 Decoders, die wichtigsten Aufgaben der Programmierbaren Logik bestehen darin, die parallelen Daten vom PC in das serielle Eingangsformat des MASCs umzuwandeln und die Konfiguration des DACs durchzuführen. Das Fifo wird benötigt um auch bei unregelmäßigem Datenfluß vom PC eine kontinuierliche Wiedergabe zu erreichen.

#### **MASC**

In Bild 3.7 ist der MASC mit seiner Beschaltung dargestellt. Die Widerstände R10 und R11 sind die Pull Up Widerstände des I<sup>2</sup>C-Busses, die restlichen Widerstände legen die Konfiguration des MASCs bei einem Reset fest. Der Quarz X2 und die Kondensatoren C13 und C14 sind die externe Beschaltung des Taktoszillators. An clk\_out steht ein Takt mit einer Frequenz von 24,576 MHz bei 48 kHz und

### 3. Realisierung

Abbildung 3.7: MASC

$32~\mathrm{kHz}$  Samplerate bzw.  $22{,}579~\mathrm{MHz}$ bei  $44{,}1~\mathrm{kHz}$  Samplerate zur Verfügung, den der MASC mit einer internen PLL erzeugt.

Über die Signale bit\_data und bit\_clk erhält der MASC seine Eingangsdaten. An den Anschlüssen sooc, sooi und sood gibt der MASC die decodierten Audiodaten im I<sup>2</sup>S-Format aus. Die Signale i2cd und i2cc entsprechen den Leitungen SDA und SCL des I<sup>2</sup>C-Buses (siehe 2.3).

Das Signal demand zeigt an, ob der MASC neue Eingangsdaten braucht, an

demand\_clk steht ein für das serielle Eingangsinterface geeigneter Schiebetakt zur Verfügung. frame\_sync zeigt an, ob gültige Daten über die I<sup>2</sup>C-Bus Schnittstelle gelesen werden können. Über rate und rate1 teilt der MASC die aktuelle Samplerate mit, in Tabelle 3.2 ist die Zuordnung von Pegeln zu Abtastraten dargestellt.

| rate | rate1 | Abtastfrequenz      |

|------|-------|---------------------|

| Low  | Low   | $44.1~\mathrm{kHz}$ |

| Low  | High  | 48 kHz              |

| High | Low   | 32 kHz              |

| High | High  | reserviert          |

Tabelle 3.2: Abtastraten

dem ist aktiv, wenn das Deemphasefilter benötigt wird. crc\_err schließlich zeigt an, daß ein Prüfsummenfehler in den Layer 3 Daten aufgetreten ist.

Da der MASC an 3,3 V betrieben wird, werden die Eingangssignale des MASCs über eine Hälfte des ICs U3, einem 74LVT244, geführt, um eine Beschädigung des MASCs durch zu hohe Logikpegel auszuschließen (siehe Bild 3.8).

#### Fifo

Das Fifo dient als Zwischenspeicher für die Layer 3 Daten und gleicht Unregelmäßigkeiten im Datenfluß vom PC aus. Als Fifo wird der Typ IDT 72V05 eingesetzt, der eine Speicherkapazität von 8 kByte bietet und an 3,3 V betrieben wird. Alternativ kann auch ein IDT 72V04 mit 4 kByte Speicher verwendet werden. Wie schon der MASC, wird auch das Fifo von der zweiten Hälfte des ICs U3 vor zu hohen Logikpegeln geschützt.

d0 bis d7 sind die Dateneingänge des Fifos, die direkt mit den Centronics-Treibern verbunden sind, fifo\_d1 bis fifo\_d8 sind die Ausgänge. Bei einem negativen Impuls an write übernimmt das Fifo ein Eingangsdatenwort in den Speicher, bei einem negativen Impuls an read wird ein Datenwort am Ausgang zur Verfügung gestellt. reset\_fifo ist der Rücksetzeingang des Fifos.

Die Ausgänge ef, hf und ff zeigen den Füllzustand des Fifos an. Die Signale bedeuten in dieser Reihenfolge leer, halb voll und ganz voll.

#### PLD

Als Programmierbarer Logikbaustein kommt der Typ 1032 aus der ispLSI-Serie von Lattice zum Einsatz. Diese Bausteine vereinigen hohe Leistungsfähig-

#### 3. Realisierung

Abbildung 3.8: PLD und Fifo

keit mit der Eigenschaft, daß sie im eingebauten Zustand programmiert werden können. Die Programmierung erfolgt über die Signale ispen, ispenset, ispenset,

Der ispLSI 1032 ist das einzige Bauteil des Layer 3 Decoders, das auf eine 5 V Versorgungsspannung angewiesen ist. Weder die ispLSI-Serie noch vergleichbare andere PLDs sind in 3 V Technik verfügbar. Während die Eingänge der 3 V ICs vor zu hohen Ausgangspegeln des PLDs geschützt werden müssen, ist zwischen 3 V Ausgängen und den Eingängen des PLDs keine Pegelanpassung nötig, da alle hier verwendeten 3 V ICs normgerechte TTL-Pegel liefern können.

Die meisten Ein- und Ausgangssignale des PLDs wurden bereits weiter oben bei anderen Schaltungsteilen beschrieben. Einer näheren Erläuterung bedürfen hier nur noch die Steuer- und Statussignale der Centronics-Schnittstelle und die Signale des externen I<sup>2</sup>S-Eingangs.

Das PLD übernimmt die Daten von den Centronics-Datenleitungen d0 bis d7 grundsätzlich bei einem negativen Impuls auf der ctr\_strobe-Leitung. Liegt dabei zusätzlich an ctr\_auto\_feed ein Low-Pegel an, so erfolgt ein Zugriff auf das Konfigurationsregister des PLDs. Ein negativer Impuls auf ctr\_rst löst einen Reset des Fifos aus und bewirkt so unmittelbar das Beenden der Wiedergabe.

Ein High-Pegel auf ctr\_busy zeigt an, daß der Decoder beschäftigt ist und keine Daten empfangen kann. Über ctr\_ack teilt das PLD dem PC den Zustand des Fifos mit. Low-Pegel bedeutet, daß das Fifo weniger als halb voll ist, was bedeutet, daß der PC einen ganzen Block von Daten senden kann, ohne bei jedem Byte den Zustand von ctr\_busy abfragen zu müssen. Über ctr\_pe und ctr\_sel kann der PC die Pegel auf den Leitungen i2cc und i2cd des I²C-Busses feststellen.

Der externe I<sup>2</sup>S-Eingang ist über den Steckverbinder J2 zugänglich. Dabei ist ex\_so0c ein Ausgang für den vom MASC erzeugten I<sup>2</sup>S-Bittakt, auf den sich eine externe I<sup>2</sup>S-Quelle synchronisieren muß, ex\_so0d und ex\_so0i sind die Datenund Worttakteingänge.

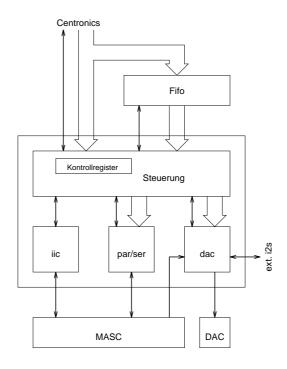

#### 3.1.5 Funktionsweise des PLDs

Die Entwicklung des Programms für den Programmierbaren Logikbausteins wurde mit dem Logikcompiler LOG/iC von ISDATA durchgeführt. Im Folgenden wird die Funktionsweise des PLDs beschrieben, die genaue Realisierung der Logik kann Anhang A.4 entnommen werden. Bild 3.9 zeigt ein Blockdiagramm des PLDs im Zusammenspiel mit den anderen Komponenten des Layer 3 Decoders.

Der interne Systemtakt des PLDs wird durch Teilung des Takts an clk\_out vom MASC durch 4 gewonnen. Die Frequenz des Systemtakts beträgt also 6,144 MHz bei 48 kHz und 32 kHz Samplerate und 5,645 MHz bei 44,1 kHz Samplerate.

Die Logik im PLD unterscheidet drei verschiedene Betriebszustände, die durch das Bitmuster im Konfigurationsregister bestimmt werden. Dies sind im einzelnen der "normale" Zustand, in dem nur die parallel-seriell Wandlung der Layer 3 Daten durchgeführt wird. Die Daten können dabei entweder direkt von der Centronics-Schnittstelle übernommen werden oder durch das Fifo zwischengespeichert werden. Im zweiten Zustand kann der DAC konfiguriert werden. In diesem Zustand wird auch festgelegt, ob der MASC oder der externe I²S-Eingang mit dem DAC verbunden wird. Der dritte Zustand ermöglicht schließlich den Zugriff auf den I²C-Bus. Der Zugriff auf den I²C-Bus ist nur dann sinnvoll, wenn das Fifo benutzt wird, da während des I²C-Zugriffs keine Layer 3 Daten vom PC gesendet werden können. Wenn das Bitmuster 0x28 in das Konfigurationsregister geschrieben wird, löst das PLD über reset\_all einen Reset des gesammten Layer 3 Decoders aus. Tabelle 3.3 zeigt die Bedeutung der bits im Konfigurationsregister und den Zustand, der sich nach einem Reset einstellt.

#### 3. Realisierung

Abbildung 3.9: Blockdiagramm des PLDs

| bit(s)  | Reset | Bedeutung                | Bemerkung                     |

|---------|-------|--------------------------|-------------------------------|

| 1       | 1     | Fifo-Modus               | Fifo wird benutzt             |

| 2       | 1     | Fifo-Füll-Modus          | vor Beginn der Wiedergabe muß |

|         |       |                          | das Fifo ganz gefüllt sein    |

| 3       | 0     | DAC-Konfiguration        |                               |

| 4, 5, 6 | -     | globaler Reset           |                               |

| 7, 8    | 0     | I <sup>2</sup> C-Zugriff |                               |

Tabelle 3.3: Konfigurationsregister

Mit dem Konfigurationsregister ist ein wesentlicher Teil des Blocks Steuerung beschrieben. Die anderen Aufgaben dieses Blocks sind die Erzeugung der Handshake-Signale an der Centronics-Schnittstelle, die Steuerung des Fifos und die Verteilung von Daten an die anderen Blöcke.

Der wichtigste Funktionsblock des PLDs ist der Block par/ser, der die parallelen Daten vom PC in das serielle Eingangsformat des MASCs umwandelt. Dieser Block besteht aus einem Schieberegister und einer State Machine, die das Schieberegister und die Datenübernahme vom Block Steuerung steuert. Daten werden gesendet, wenn gültige Daten vorhanden sind und der MASC sie mit demand an-

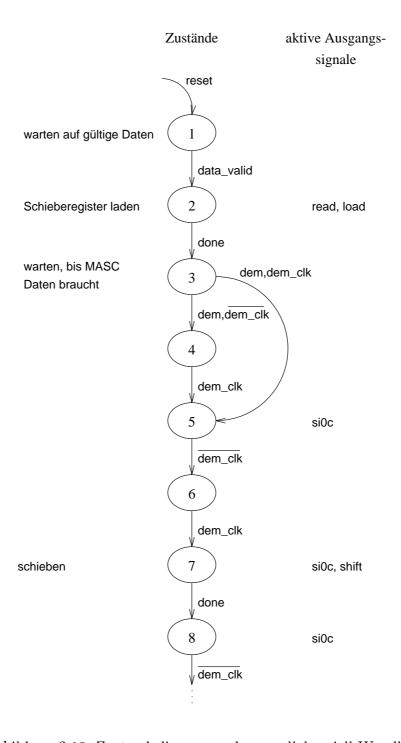

fordert. Bild 3.10 zeigt einen Ausschnitt aus dem Zustandsdiagramm der State Machine.

Abbildung 3.10: Zustandsdiagramm der parallel-seriell Wandlung

Die State Machine ist von den Eingangssignalen data\_valid, dem, dem\_clk und done abhängig. Mit dem Signal data\_valid teilt der Block Steuerung mit, daß gültige Daten vorhanden sind, dem und dem\_clk entspechen den Signalen demand und demand\_clk vom MASC und done bedeutet, daß das Schieberegister eine Lade- oder Schiebeoperation beendet hat. Die State Machine erzeugt die Signale shift, load, read und siOc. Mit shift bzw. load wird eine Schiebe- bzw. Lade-operation des Schieberegisters ausgelöst, read teilt Steuerung mit, daß ein Datum übernommen wurde, siOc ist der Schiebetakt für den MASC, der mit demand\_clk synchronisiert ist. Wenn die 8 bits eines Bytes übertragen sind, beginnt der Zyklus der State Machine wieder im Zustand 1.

Der Block dac ist dem Block par/ser sehr ähnlich, zur seriellen Konfiguration des DACs wird wieder eine Kombination aus Schieberegister und State Machine benötigt. Bei jedem Reset wird der DAC mit Default-Werten konfiguriert. Zusätzlich kann im Block dac zwischen dem I<sup>2</sup>S-Signal vom MASC und dem externen I<sup>2</sup>S-Signal gewählt werden. Schließlich wird der Takt master\_clk für den DAC erzeugt. Die Frequenz von master\_clk muß gleich der 256-fachen Samplerate sein, der MASC stellt an clk\_out einen Takt zur Verfügung, der bei 48 kHz und 44,1 kHz Samplerate die 512-fache Frequenz der Samplerate, bei 32 kHz die 768-fache Frequenz hat. clk\_out wird also je nach Abtastfrequenz durch 2 oder durch 3 geteilt.

Der Block iic ist der einfachste Block im PLD. Er besteht im wesentlichen nur aus zwei Open-Collector Treibern, die durch Tri-State Ausgänge nachgebildet werden. Im I<sup>2</sup>C-Modus kann der PC die Pegel auf den Leitungen i2cd und i2cc über die Centronics-Datenleitungen d0 und d1 beeinflussen und die tatsächlichen Pegel über ctr\_sel und ctr\_pe lesen. Die Abwicklung des I<sup>2</sup>C-Bus Protokolls erfolgt durch die PC-Software. Wenn das PLD sich nicht im I<sup>2</sup>C-Modus befindet, sind die Treiber auf Tri-State geschaltet, was High-Pegel auf i2cd und i2cc zuf Folge hat. Außerdem zeigt dann ctr\_sel den Zustand von frame\_sync an.

## 3.1.6 Externe Verbindungen

Zum Abschluß der Schaltungsbeschreibung wird hier noch die Belegung der einzelnen Steckverbindungen angegeben:

**CON1** ist ein 25-poliger Sub-D Stecker, mit dem der Layer 3 Decoder an die Centronics-Schnittstelle eines PCs angeschlossen wird. Die Beschaltung entspricht dem Centronics-Standard.

**CON2** ist eine Hohlstiftbuchse, über die der Decoder mit einer Versorgungsspannung von 3 V bis 6 V verbunden wird. Der Pluspol der Spannung liegt dabei am Stift, der Minuspol am äußeren Anschluß.

**CON3** und **CON4** sind die Audio-Ausgänge des Decoders, sie sind als Cinch-Buchsen ausgeführt. CON3 überträgt den linken, CON4 den rechten Audiokanal.

${f J1}$  Über die 8-polige Buchse J1 kann das PLD programmiert werden. Die Belegung ist in Tabelle 3.4 dargestellt.

| Pin | Signal    | Pin | Signal   |

|-----|-----------|-----|----------|

| 1   | + 5 V     | 2   | isp_sdo  |

| 3   | isp_sdi   | 4   | ispen    |

| 5   | isp_reset | 6   | isp_mode |

| 7   | isp_sclk  | 8   | GND      |

Tabelle 3.4: Belegung von J1

**J2** An J2 sind der I<sup>2</sup>S-Ein- und Ausgang sowie einige Statussignale zugänglich. Die Belegung der 14-poligen Buchse zeigt Tabelle 3.5.

| Pin | Signal  | Bemerkung                    |

|-----|---------|------------------------------|

| 1   | GND     |                              |

| 2   | + 5 V   |                              |

| 3   | ex_so0c | Schiebetaktausgang           |

| 5   | ex_so0i | Worttakteingang              |

| 7   | ex_so0d | Dateneingang                 |

| 4   | i2s_c   | $I^2S$ -Ausgang,             |

| 6   | i2s_i   | siehe Beschreibung des DACs, |

| 8   | i2s_d   | Abschnitt 3.1.3              |

| 9   | rate    | siehe                        |

| 11  | rate1   | Tabelle 3.2                  |

| 10  | dem     | Deemphase                    |

| 12  | crc_err | Prüfsummenfehler             |

| 13  | GND     |                              |

| 14  | + 3,3 V |                              |

Tabelle 3.5: Belegung von J2

## 3.2 Software

Die Software zum Layer 3 Decoder ermöglicht die Wiedergabe von Layer 3 Files und die Steuerung der I<sup>2</sup>C-Bus Schnittstelle. Über die I<sup>2</sup>C-Bus Schnittstelle kann die Lautstärke eingestellt werden, es kann ein Programm in den MASC geladen werden und die Informationen aus dem Header der Layer 3 Daten sowie die Ancillary Daten können vom MASC gelesen werden.

Bei der Entwicklung der Software wurde vor allem Wert darauf gelegt, alle Eigenschaften der Hardware aufzuzeigen und nicht auf eine besonders einfache Bedienung oder eine schöne Benutzeroberfläche. Das Programm ist in der Sprache C geschrieben, einige zeitkritische Programmteile in Assembler.

### 3.2.1 Bedienung der Software

Das Programm zur Wiedergabe von Layer 3 Files wird unter MS-DOS mit der Kommandozeile

```

LPT Layer-3-File [-Optionen]

```

aufgerufen.

```

LPT playing file: data\guitar.bit

Volume: -0.0 dB

Header Information:

III Emphasis:

Laver:

none

Sampling Frequency:

44.1 kHz

no copyright,

сору

Bitrate:

128 kbps

Mode:

stereo

Mode Extension:

normal

Ancillary Data:

07 10 c1 00 05 07 00 c0 a5 05 0f 00 00 a5 07 93

lpt version 1.7. Replay on lpt1 (address 378)

```

Abbildung 3.11: Typischer Bildschirm

Werden keine Optionen angegeben, wird das angegebene Layer 3 File wiedergegeben, aber weder die Header Informationen noch Ancillary Daten werden angezeigt. Die Anzeige der Header Informationen kann durch Angeben der Option-hed beim Programmaufruf eingeschaltet werden, die Anzeige von Ancillary Daten durch Angeben von -anc. Abbildung 3.11 zeigt das typische Erscheinungsbild des Programms. Der Aufruf dafür lautete:

```

LPT data\guitar.bit -hed -anc -hex

```

Während der Wiedergabe von Layer 3 Files reagiert das Programm auf folgende Tasten:

- Esc: Das Programm wird beendet.

- +/-: Die Wiedergabelautstärke wird erhöht/verringert.

- r: Ein Reset des Decoders wird ausgelöst.

- h: Die Darstellungsform der Ancillary Daten wird zwischen Text- und Hexadezimaldarstellung umgschaltet.

## 3.2.2 Kommandozeilenoptionen

Wird das Programm LPT mit ungültigen Parametern aufgerufen, so wird folgender Hilfetext ausgegeben:

```

LPT bitstream -switches

usage:

switches:

display this help message

-lpt xxx

number of lpt port (default=1)

-dl xxx

download program file for MASC

reset on start

-\mathbf{r}

display header data

-hed

display ancillary data (if -hed is set)

-anc

display ancillary data as hexadecimal value

-hex

DAC config value

-dac xxx

```

Die Optionen bedeuten im Einzelnen:

-lpt: Die Nummer der Druckerschnittstelle, an die der Layer 3 Decoder angeschlossen ist, wird angegeben. Gültige Werte für xxx sind 1, 2 und 3. Wird diese Option nicht angegeben, wird die Druckerschnittstelle Nummer 1 verwendet.

-d1: Ein Programm wird in das RAM des MASCs geladen. xxx steht für den Dateinamen des Programms. Die Programmdatei muß eine ASCII Textdatei mit

folgendem Inhalt sein: In der ersten Zeile steht I2C-Download, in den folgenden Zeilen jeweils eine vierstellige Hexadezimalzahl.

-r: Vor Beginn der Wiedergabe wird ein Reset des Decoders ausgelöst.

-hed: Die Header Informationen der Layer 3 Daten werden über den I<sup>2</sup>C-Bus gelesen und am Bildschirm dargestellt.

-anc: Zusätzlich zu den Header Informationen werden auch die Ancillary Daten gelesen und dargestellt. Diese Option hat nur dann eine Wirkung, wenn auch -hed angegeben ist.

-hex: Die Ancillary Daten werden als hexadezimale Werte dargestellt. Zur Laufzeit des Programms ist eine Umschaltung zwischen hexadezimaler und Textdarstellung mit der Taste h möglich.

-dac: Der DAC wird konfiguriert. xxx muß eine zweistellige Hexadezimalzahl sein, die ein 7-stelliges Bitmuster repräsentiert. Die 5 niederwertigsten bits entsprechen den bits B1 bis B5 von Abbildung 3.6 auf Seite 15. Die Bedeutung der einzelnen bits ist in Tabelle 3.6 erläutert.

| bit(s) | Reset | Bedeutung |                                                 |  |

|--------|-------|-----------|-------------------------------------------------|--|

| 1, 2   | 1, 0  | 0, 0      | 16 bits pro Kanal                               |  |

|        |       | 0, 1      | 24 bits pro Kanal                               |  |

|        |       | 1, 0      | 32 bits pro Kanal                               |  |

|        |       | 1, 1      | 64 bits pro Kanal                               |  |

| 3      | 0     | 0         | Audiodaten sind gegebüber i2s_i links           |  |

|        |       |           | ausgerichtet                                    |  |

|        |       | 1         | Audiodaten sind gegebüber i2s_i rechts          |  |

|        |       |           | ausgerichtet                                    |  |

| 4      | 1     | 0         | ,normales' Datenformat                          |  |

|        |       | 1         | I <sup>2</sup> S-Datenformat                    |  |

| 5      | 0     | 0         | 18 bit Audiodaten                               |  |

|        |       | 1         | 16 bit Audiodaten                               |  |

| 6      | 0     | 0         | DAC erhält über i2s_c Deemphasesignal           |  |

|        |       | 1         | DAC erhält über i2s_c Schiebetakt               |  |

| 7      | 0     | 0         | DAC erhält Daten vom MASC                       |  |

|        |       | 1         | DAC erhält Daten vom externen I <sup>2</sup> S- |  |

|        |       |           | Eingang                                         |  |

Tabelle 3.6: Konfiguration des DACs

Die Konfiguration, die der Decoder bei jedem Reset einstellt, entspricht der Hexadezimalzahl 09. Wenn man eine externe Quelle, die dasselbe Datenformat wie der

MASC liefert, wiedergeben will, so muß für xxx 49 angegeben werden. Weitere Angaben zur Wirkung der bits 1 bis 5 finden sich im Datenblatt des CS 4331.

### 3.2.3 Programmbeschreibung

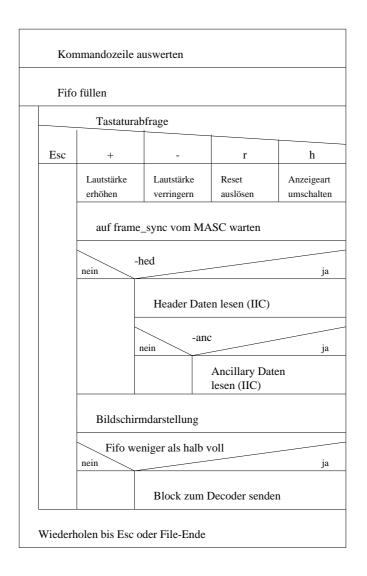

Wie schon beim PLD wird auch hier nur die grundsätzliche Struktur des Programms aufgezeigt, die genaue Realisierung kann Anhang B entnommen werden. Abbildung 3.12 zeigt die Struktur des Hauptprogramms.

Abbildung 3.12: Programmstruktur

Zuerst wird die Kommandozeile ausgewertet, bei einer fehlerhaften Kommandozeile wird ein Hilfetext ausgegeben. In diesem Programmteil findet auch ein

eventueller Programmdownload in den MASC statt. Vor Beginn der Hauptschleife wird das Fifo aufgefüllt. In der Hauptschleife erfolgt zuerst die Tastaturabfrage, dann werden je nach Kommandozeilenoptionen Header und Ancillary Daten gelesen und am Bildschirm dargestellt. Am Ende der Hauptschleife wird ein neuer Block Layer 3 Daten an den Decoder gesendet, wenn das Fifo weniger als halb voll ist.

Die Funktionen des C-Programms sind auf verschiedene Dateien aufgeteilt. Besonders wichtig sind die Dateien masccent.c und iic.c. In masccent sind die Funktionen zum Zugriff auf das Konfigurationsregister des Decoders, zur Konfiguration des DACs und zum Senden von Layer 3 Daten an den Decoder definiert. Die Funktionen zum Lesen und Schreiben auf den I<sup>2</sup>C-Bus sind in der Datei iic.c definiert.

Fast alle Funktionen sind in der Sprache C programmiert. Die Funktionen zum Senden von Layer 3 Daten an den Decoder sind in Assembler programmiert um hier die maximale Geschwindigkeit zu erreichen. Da der verwendete C-Compiler von Borland dafür bekannt ist, bei Bitschiebeoperationen sehr ineffektiven Code zu erzeugen, sind auch die Funktionen zum Lesen und Schreiben auf den I<sup>2</sup>C-Bus in Assembler programmiert, da zu der hier notwendigen parallel-seriell Wandlung viele Bitschiebeoperationen benötigt werden.

## 4.1 Stromversorgung

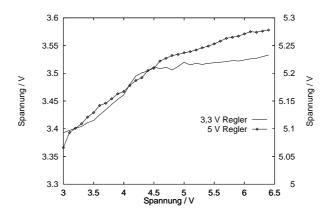

Da die Schaltreglerbausteine MAX 877/8 bisher am IIS noch nie verwendet wurden, wurde die damit realisierte Spannungsregelung meßtechnisch untersucht. Abbildung 4.1 zeigt die Ausgangsspannungen der beiden Regler in Abhängigkeit von der Eingangsspannung.

Abbildung 4.1: Regelung der Versorgungsspannungen

Bei einer Änderung der Eingangsspannung von 3 V auf 6,4 V ändert sich die Ausgangsspannung des 3,3 V Reglers um 0,15 V, die des 5 V Reglers um 0,21 V. Diese Messung wurde unter realen Betriebsbedingungen an im Decoder eingebauten Reglern durchgeführt. Der 3,3 V Regler wird mit ca. 120 mA bis 150 mA belastet, der 5V Regler muß ca. 150 mA bis 180 mA Strom liefern.

Abbildung 4.2a zeigt die der 5 V Spannung überlagerte Störspannung. Die Spitze-Spitze-Spannung der Störung beträgt etwa 180 mV, die Frequenz ca. 60 kHz. Bild 4.2b zeigt das Spektrum dieser Störung. Man erkennt neben der starken Spektrallinie bei 60 kHz weitere Linien, darunter auch zwei bei 8 kHz und 16 kHz, die im hörbaren Frequenzbereich liegen und daher für Anwendungen im Audiobereich besonders kritisch sind.

Abbildungen 4.2a,b: Störungen auf den Versorgungsspannungen

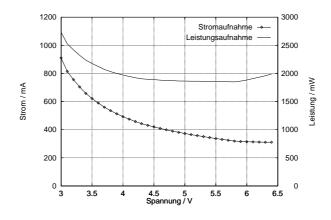

In Bild 4.3 ist die Stromaufnahme und die Leistungsaufnahme des Layer 3 Decoders in Abhängigkeit von der Versorgungsspannung dargestellt. Wie für die Schaltregler zu erwarten, sinkt die Stromaufnahme mit steigender Versorgungsspannung, bei 5 V beträgt der aufgenommene Strom 370 mA. Die Leistungsaufnahme erreicht bei 5,8 V mit 1,85 W ein Minimum, im Bereich zwischen 4,0 V und 6,4 V bleibt die Leistung unter 2 W.

Abbildung 4.3: Stromaufnahme

Man erkennt, daß die Stromaufnahme dieses Decoders höher ist als die des alten Decoders. Der Grund dafür ist die Verwendung des leistungsfähigeren PLDs ispLSI 1032 an Stelle des ispLSI 1016. Man erhält dafür aber auch eine deutlich höhere Funktionalität (I<sup>2</sup>C-Bus, I<sup>2</sup>S-Eingang). Vergleicht man die Leistungsaufnahme, so ist die Leistungsaufnahme des neuen Decoders geringer als die des alten, da der alte Decoder zur Spannungsregelung einen Linearregler von Typ 7805 verwendet, der eine Eingangsspannung von mindestens 8 V benötigt. Die

Leistungsaufnahme des alten Decoders beträgt daher mindestens 2,4 W, die des neuen ist bei Versorgungsspannungen zwischen 4 V und 6 V kleiner als 2 W.

## 4.2 Audioqualität des DACs

Alle Messungen am DAC wurden mit einem Audio Analyzer UPD von Rohde & Schwarz durchgeführt. Dieser Audio Analyzer verfügt über einen universellen seriellen Digitalausgang, der in sehr vielfältiger Weise konfiguriert werden kann. Um Messungen am Layer 3 Decoder durchzuführen, ist der Digitalausgang des UPDs mit dem I<sup>2</sup>S-Eingang des Decoders wie in Tabelle 4.1 gezeigt zu verbinden.

| Signal   | UPD Serial Out | L 3 Decoder J2 |

|----------|----------------|----------------|

| GND      | 7              | 1              |

| Bittakt  | 4              | 3              |

| Worttakt | 10             | 5              |

| Daten    | 6              | 7              |

Tabelle 4.1: Verbindung mit UPD

Der Generator des UPDs ist wie in Tabelle 4.2 gezeigt einzustellen.

Output: Serial Mux

Channel(s):  $2 \equiv 1$

Sample Frq: EXTERN

Wordlength: 32 Wordoffset: -1 Audio Bits: 18

Bitclock: RISING

WordselCh1: LOW

Bit Order: MSB First

Tabelle 4.2: Einstellungen des UPDs

Um den externen I<sup>2</sup>S-Eingang des Decoders zu aktivieren, muß das Programm LPT mit der Option -dac 49 aufgerufen werden:

LPT Layer-3-File -dac 49

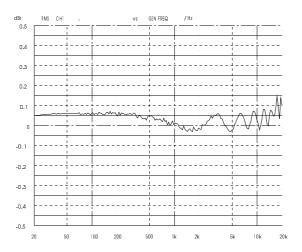

Abbildung 4.4 zeigt den Frequenzgang des DACs. Die Abweichungen bleiben geringer als 0,1 dB, nur am oberen Ende des Frequenzbereiches ist die Abweichung

geringfügig größer. Die Messung bestätigt die Angaben des Datenblatts des CS 4331.

Abbildung 4.4: Frequenzgang des DACs

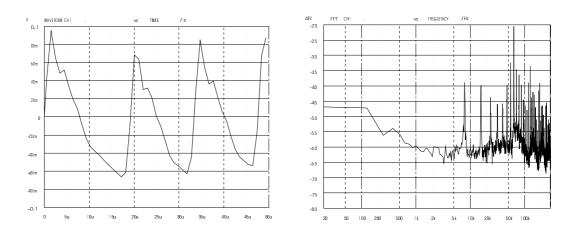

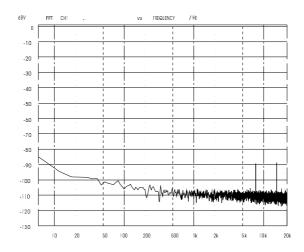

In Bild 4.5 ist das Spektrum am Ausgangs des DACs dargestellt, wenn der DAC mit digital Null angesteuert wird. Das Rauschen ist im hörbaren Frequenzbereich deutlich niedriger als -90 dBV. Man erkennt 2 Linien bei 8 kHz und 16kHz. Dies sind Störungen, die von der Versorgungsspannung eingekoppelt werden. Die Störungen sind mit -90 dBV ausreichend gering.

Abbildung 4.5: Ausgangsspektrum bei digital Null am Eingang

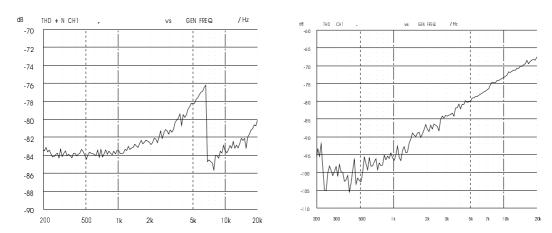

Abbildung 4.6a zeigt das Ergebnis einer THD+N Messung. THD+N bedeutet Total Harmonic Distortion plus Noise. Bei dieser Messung wird der DAC mit

einem digitalen Sinussignal angesteuert, im Ausgangssignal wird diese Frequenz herausgefiltert, das verbleibende Signal ist ein Maß für die Summe aus Rauschen und Verzerrungen. Im Frequenzbereich unter 1 kHz erreicht der CS 4331 mit -83 dB durchaus zufriedenstellende Werte, das Datenblatt gibt einen Wert von -88 dB bei 1 kHz an. Über 1 kHz steigen die Verzerrungen des DACs stark an, vor allem die dritte Harmonische.

Abbildungen 4.6a,b: Verzerrungen des DACs

Die selektive Messung der dritten Harmonischen ist in Bild 4.6b dargestellt. Ab etwa 1 kHz steigt die Amplitude dieser Oberwelle mit 20 dB pro Dekade an. Da ab einer Grundfrequenz von 6,6 kHz die dritte Harmonische nicht mehr in die Meßbandbreite von 20 kHz fällt, kommt es zu dem Sprung in der THD+N Messung. Das Ansteigen der dritten Harmonischen ist nicht als besonders schwerwiegend zu bewerten, da diese Verzerrung nur bei entsprechend starkem Grundton auftritt und dann gering genug bleibt, um von diesem Grundton verdeckt zu werden (siehe Abschnitt 2.1.1).

## 4.3 Erfahrungen mit Hard- und Software

Von dem Layer 3 Decoder wurden bis jetzt 3 Prototypen aufgebaut. Zur Zeit ist jedoch nur ein Prototyp funktionsfähig, ein Decoder wurde bei Messungen durch einen Kurzschluß beschädigt, ein anderer vermutlich durch elektrostatische Entladung.

Das Zusammenspiel von Hard- und Software wurde auf verschiedenen Rechnern vom 386/16 bis zum Pentium 90 getestet und funktionierte stets reibungslos. Der Decoder konnte alle am IIS vorhandenen Layer 3 Files ohne hörbare Störungen wiedergeben.

Der Zugriff auf den I<sup>2</sup>C-Bus arbeitet beim Programm-Download, bei der

Lautstärkeeinstellung und beim Lesen der Header Daten fehlerlos. Ancillary Daten lassen sich jedoch nicht korrekt lesen. Da der I<sup>2</sup>C-Bus bei allen anderen Zugriffen einwandfrei arbeitet, ist der Fehler bei den Ancillary Daten wohl beim MASC zu suchen.

# 5. Zusammenfassung und Ausblick

## 5.1 Technische Daten

Als Zusammenfassung von Kapitel 4 sind hier noch einmal die gemessenen technischen Daten des Layer 3 Decoders aufgeführt:

Versorgungsspannung 3–6 V DC

Stromaufnahme 370 mA bei 5 V

Leistungsaufnahme < 2 W bei 4–6 V

Harmonische Verzerrungen und < -83 dB bei 1 kHz

Rauschen (THD+N)

Tabelle 5.1: Technische Daten

Die Wiedergabe von Layer 3 Files ist mit allen IBM PC kompatiblen Rechnern möglich.

## 5.2 Verbesserte Stromversorgung

Es hat sich herausgestellt, daß für die Schaltreglerbausteine teilweise erhebliche Lieferzeiten zu erwarten sind. In dieser Studienarbeit konnte deshalb der MAX 877 nicht eingesetzt werden. Er wurde durch den Baustein MAX 879 ersetzt, dessen Ausgangsspannung durch zwei Widerstände eingstellt werden kann. Da diese Widerstände auf der Platine nicht vorgesehen waren, mußten sie frei verdrahtet werden.

Der MAX 879 kann sowohl für den MAX 877 als auch für den MAX 878 als Ersatz dienen. Da hierfür nur sehr geringe Änderungen an der Schaltung nötig sind, sollte diese Möglichkeit bei zukünftigen Produkten vorgesehen werden.

#### 5. Zusammenfassung und Ausblick

Abbildung 5.1: Verbesserte Stromversorgung

| U8  |          |                       | U9  |            |                       |

|-----|----------|-----------------------|-----|------------|-----------------------|

|     | MAX 877  | MAX 879               |     | MAX 878    | MAX 879               |

| R24 | entfällt | $24~\mathrm{k}\Omega$ | R26 | entfällt   | $15~\mathrm{k}\Omega$ |

| R25 | entfällt | $1~\mathrm{k}\Omega$  | R27 | $\Omega$ 0 | $1~\mathrm{k}\Omega$  |

Tabelle 5.2: Zusätzliche Widerstände für verbesserte Stromversorgung

Abbildung 5.1 zeigt die geänderte Stromversorgungsschaltung, in Tabelle 5.2 sind die Werte der zusätzlichen Widerstände für alle Bestückungsvarianten zusammengefaßt.

## 5.3 Preiswertere Version des Decoders

Das in diesem Decoder eingesetzte CPLD vom Typ ispLSI 1032 ist ein recht teueres Bauelement. Der Preis beträgt zur Zeit etwa 75 DM, das ist deutlich mehr als der Preis für den MASC (ca. 30 bis 40 DM).

Wenn man auf die Möglichkeit ein externes I<sup>2</sup>S-Signal einspeisen zu können und das Deemphasefilter verzichten kann, dann muß der DAC nicht mehr konfiguriert

werden und die entsprechende Logik kann entfallen. Die restliche Logik paßt dann in ein CPLD vom Typ ispLSI 1024, das mit 39 DM deutlich preiswerter als das ispLSI 1032 ist.

Die Einspeisung eines externen I<sup>2</sup>S-Signals ist vor allem für Messungen am DAC wichtig, eine Deemphase ist zwar im MPEG-Standard vorgesehen, wird aber in der Praxis kaum angewendet. Der Decoder kann also ohne schwerwiegende Einschränkung der Funktionalität auch preiswerter hergestellt werden.

Im Anhang C ist eine entsprechend modifizierte Schaltung genauer beschrieben.

### 5.4 Fazit

Der Layer 3 Decoder hat sich als funktionsfähig und betriebssicher erwiesen. Er zeichnet sich durch eine geringe Leistungsaufnahme aus, einer Serienproduktion, eventuell mit den Modifikationen nach 5.2 und 5.3, steht nichts im Wege.

Die mit dem MASC, den Schaltreglern und dem DAC gemachten Erfahrungen können am IIS sicher weiter nutzbringend angewendet werden.

Für die Zukunft verbleiben folgende Aufgaben:

- Von ITT ist ein MAS 3503 D angekündigt, der außer Layer 3 auch die Layer 1 und 2 decodieren kann. Wenn dieser Prozessor verfügbar wird, sollte er auch in diesem Decoder eingesetzt werden.

- Wenn ausreichend leistungsfähige CPLDs in 3 V Technik erhältlich werden, kann ein Re-Design in reiner 3 V Technik erstellt werden. Im wesentlichen können dann die ICs U3 und U8 ersatzlos entfallen.

- Der Fehler bei der Übertragung von Ancillary Daten sollte näher untersucht werden. Wahrscheinlich ist der Fehler beim MASC zu suchen.

- Die Software könnte bedienungsfreundlicher gestaltet werden. Auch ein Programm unter MS Windows ist denkbar.

# Abkürzungen

CD Compact Disc

CPLD Complex PLD

DAB Digital Audio Broadcasting

DAC Digital Analog Converter

DCC Digital Compact Casette

I<sup>2</sup>C, IIC Inter IC

I<sup>2</sup>S Inter IC Sound

IIS Institut für Integrierte Schaltungen

kbps kilobits per second

MPEG Motion Picture Experts Group

MSB Most Significant Bit

PLD Programmable Logic Device

PLL Phase Locked Loop

RAM Random Access Memory

ROM Read Only Memory

SMD Surface Mounted Device

TTL Transistor Transistor Logik

# Literaturverzeichnis

- [1] ISO/IEC JTC1/SC29/WG11 MPEG, International Standard IS 11172-3. Coding of moving pictures and associated audio for digital storage media at up to about 1.5 Mbit/s, Part 3: Audio, 1993.

- [2] ERNST, MARTIN UND STILLER, ANDREAS. PC-Bausteine, Details über die Centronics-Parallel-Schnittstelle. In c't magazin für computer technik, 1988, Heft 6, Seite 166–176.

- [3] Lattice Semiconductor. Introduction to pLSI and ispLSI Families. In *Lattice Data Book*, Lattice, 1994, Seite 2-1–2-10.

- [4] Phillips Bauelemente. I<sup>2</sup>C-bus specification. In  $I^2C$ -Bus-Schaltungen für professionelle Anwendungen, Phillips, 1989, Seite 9–31.

- [5] POPP, HARALD. Der Ton macht die Musik. In *Elektronik*, 1995, Heft 5, Seite 110–117.

- [6] RISTOV, KEN UND PERNA, STEVE. Mixing it up with 3.3 Volts. In Low-Voltage-Logic LVT, LVC, ALVC and LV Families Data Book, Texas Instruments, 1994, Seite 4-3-4-7.

- [7] TIETZE, ULRICH UND SCHENK, CHRISTOPH. *Halbleiter-Schaltungstechnik*. Springer, Berlin Heidelberg New York, 10. Aufl., 1993.

- [8] WITTE, FRANZ-OTTO, DIETZ, MARTIN UND SINNHÖFER, WERNER. Single Chip Implementation of an ISO/MPEG Layer III Decoder. 96th AES Convention, Amsterdam, 1994, preprint 3805.

- [9] WITTE, FRANZ-OTTO UND SINNHÖFER, WERNER. Musik vom Himmel, Ein ADR-Decoder auf Basis des MASC-Prozessorkerns. In *Elektronik*, 1995, Heft 17, Seite 94–104.

- [10] ZWICKER, EBERHARD. *Psychoakustik*. Springer, Berlin Heidelberg New York, 1982.

Literatur verzeichnis